英飞凌高效率100W USB-PD方案XDPS2201

2021-03-16 classification:行业新闻

围绕装备有主流快充协议USB-PD充电器设计,我们正在进行技术文章的四期连载。系列文章从提高效率、加速产品开发、优化性能、降低整体成本等方面,为大家详细解读。

作为本系列的最终章,我们将为大家介绍效率高达94%的100WUSB-PD解决方案。

更大的电池容量和更短的充电时间需求,不断提高对于充电器功率的要求。在小尺寸中实现大功率颇具挑战性,人们为此提出了各种各样的创新方案,包括零电压开关(ZVS)拓扑结构、高性能开关、创新的封装方式以及使用宽禁带材料等,以满足相应设计要求。

本文介绍了一种100W的USB-PD解决方案,并解释了它如何利用电源开关和新型拓扑结构来实现94%的效率和23W/in3的功率密度。

为了达到更高的功率密度,需要选择合适的拓扑结构、规格尺寸和先进的控制技术。纵观当前的大功率移动充电器市场,存在着多种针对大功率USB-PD充电器的解决方案,包括PFC+QR和PFC+LLC。然而,这些解决方案也存在一定局限性,限制了其得到广泛应用,例如:QR无法实现软开关,LLC拓扑结构难以用于可变输出电压设计。

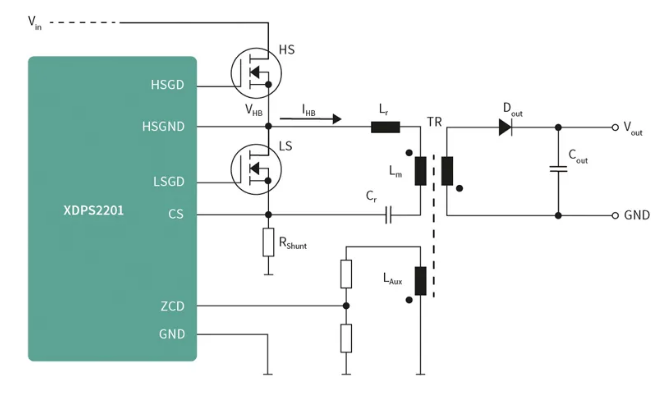

针对上述情况,英飞凌推出了一种新的非对称半桥混合型反激拓扑结构(如图1)。半桥与串联电容器共同驱动传统的反激变压器。反激变压器的主电感和串联电容器形成谐振回路,用于实现半桥开关的ZVS特性,并在反激变压器的常规退磁阶段提供谐振功率传输。在正常运行期间,充电周期和相关功率通过峰值直流电流控制,而退磁阶段通过定时控制,以确保适当的负预磁化,从而满足半桥开关所需的ZVS条件。

图1:非对称半桥反激拓朴的简化示意图

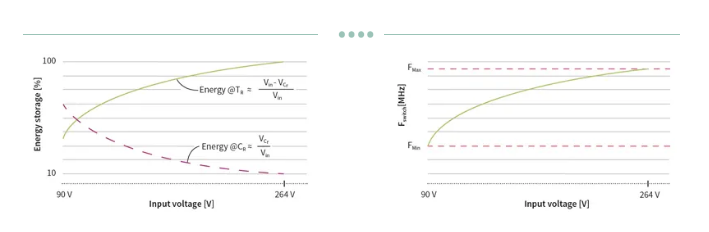

初级侧的电源电路通过LC谐振回路实现,该回路由类似于LLC转换器的半桥驱动。谐振电感器Lr为串联电感,它既可以是变压器漏感,也可以是变压器漏感加外部电感,而Lm则代表变压器主电感。通过将谐振电容器Cr和变压器的初级线圈连接于正节点和半桥中点之间,也可以实现相同的转换效果。当高侧开关HS导通时,能量将存储于Cr和Lm中,并且各自存储的能量将随输入电压和开关频率而变化(如图2所示)。

图2:储能分布和频率变化示意图

当高侧开关HS断开时,变压器中的电流将迫使半桥中点VHB下降,直至低侧开关的体二极管钳位电压为止。然后,低侧开关将在零电压时导通,与此同时,变压器相位反转,能量转移至次级侧。当低侧开关断开时,上一阶段变压器中感应的负电流将迫使半桥中点VHB升高其电压,直至高侧开关HS的体二极管钳位电压为止,类似于上一个阶段。在ZVS条件下,HS打开,而LS关闭,但变压器谐振回路中的电流仍为负,这意味着谐振回路中的多余能量将被送回输入端。

与其他反激拓扑结构相比,混合反激变压器需要存储的能量比较少,因此有助于减小充电器的尺寸。

混合反激可以在初级侧实现完全的ZVS,而在次级侧实现完全的ZCS,并且泄漏能量也可以回收,从而提高效率。

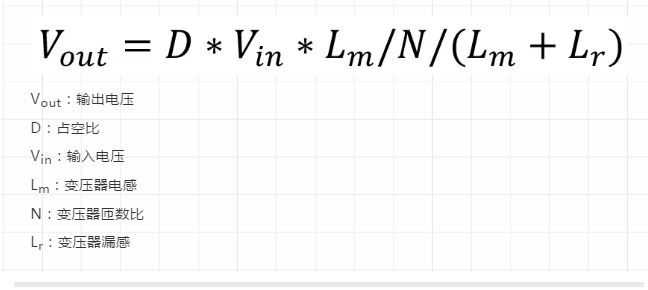

如以下公式,输出电压将随占空比变化。对于混合反激式来说,实现宽电压范围的输出要容易得多,由此克服了LLC拓扑结构在宽电压输出应用中的局限性。

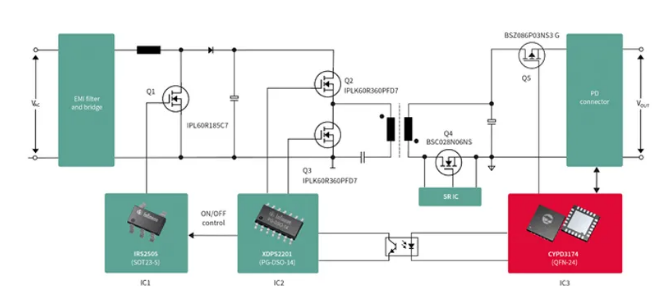

完整的解决方案如图3所示。PFC级采用临界导通模式IRS2505和ThinPAK封装IPL60R185C7CoolMOS™,而DC-DC级则采用数字PWM控制器XDPS2201和IPLK60R360PFD7。同时,BSC028N06NS用作同步整流开关(将来可以换成专门针对充电器同步整流用的低压ISZ0702NLS以进一步提升性价比),协议控制器为CYPD3174,而p-channelMOSBSZ086N03NS3用作输出安全开关。

图3:100WUSB-PD解决方案框图

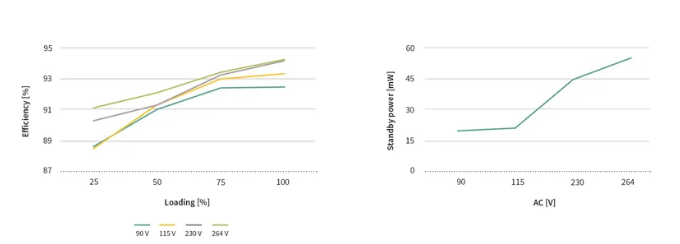

通过这种设置,效率峰值可以达到94%,并且待机功耗低于60mW。

图4:效率和待机功耗曲线

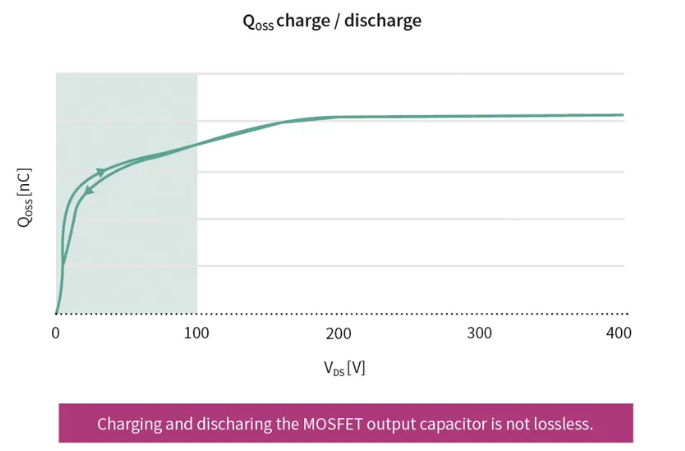

软开关技术使器件能够在ZVS下运行,即MOSFET仅在其漏源电压达到0V(或接近于0V)后才导通。这种策略可以消除器件的导通损耗,而导通损耗通常是造成总开关损耗的主要因素。遗憾的是,由于输出电容的“非无损”特性,所有高压SJMOSFET都会遭受另外一种损耗,即在MOSFET输出电容(Coss)先充电后放电时,都会有部分能量损失。因此,即使在ZVS条件下运行,也无法回收存储于输出电容中的全部能量(Eoss)。这种现象与Coss的滞回特性有关,在执行Coss充电/放电周期时可以借助较大的信号测量观察到这种现象。正因如此,此类损耗通常被称为Coss滞回损耗(Eoss,hys)。

图5:SJMOSFET的Qoss充电/放电周期

得益于英飞凌先进的SJ技术,CoolMOS™PFD7系列进一步降低了滞回损耗,从而有助于进一步提高效率。

结论

基于数字XDPS2201的ZVS混合反激式,可以在不同的输入电压和输出电流条件下实现ZVS和ZCS。此外,它还可以回收变压器漏感的能量。高性能的功率MOSFET有助于在60mmx40mmx18mm尺寸的100WUSB-PD设计实现高达94%的效率。

图6:外形小巧、效率高达94%的英飞凌100WUSB-PD参考设计

确保高性能的关键:选择合适的拓扑结构

为什么首选混合反激拓扑结构?

英飞凌的100WUSB-PD参考设计

最高效率:选择适当的高压MOSFET至关重要

出错文件:root/en/news_show.php

出错行数:188

错误信息:Undefined index: title_en

错误级别:8

Customer service

Customer service